지난 주요뉴스 한국경제TV에서 선정한 지난 주요뉴스 뉴스썸 한국경제TV 웹사이트에서 접속자들이 많이 본 뉴스 한국경제TV 기사만 onoff

-

쿠팡 4분기 이익 '급감' 이면은…기저효과·원가증가·투자확대 2026-03-04 06:15:00

개선폭이 커지는 효과를 기대할 수 있다. 다만 회사가 관련 비용의 구체적인 세부 항목을 공개하고 있지는 않아 구체적인 실적 부진 원인을 단정하기는 어렵다. 거랍 아난드 최고재무책임자(CFO)가 콘퍼런스콜에서 그간의 마진 확대 추세가 올해 '중단'(Disrupted)될 것"이라고 언급한 점 등을 감안했을 때 사고...

- 뉴스 > 경제

- 바로가기

-

대만 매체 "TSMC 건설중·올해 착공 예정 공장 대만에 10여곳" 2026-02-24 11:48:02

생산 계획인 1공장(P1)의 환경영향평가가 통과되면 5월부터 착공하고, 남부과학단지 3기에 CoWoS 첨단 패키징 공장, 자이과학단지에는 올해 2개의 패키징 공장 건설에 나설 계획이라고 전했다. 나노는 반도체 회로 선폭을 의미하는 단위로, 선폭이 좁을수록 소비전력이 줄고 처리 속도가 빨라진다. jinbi100@yna.co.kr...

- 뉴스 > 정치

- 바로가기

-

[마켓PRO] Today's Pick : "삼성전자, 천고삼비, 유리한 사업환경 지속 전망" 2026-02-24 08:32:51

기존 23만원에서 25만원으로 상향 조정. 국내 제한적인 마진 개선폭 감안하여 할증률변경 적용하여 산정. 2026년에도 주요 고객사 업황호조에 따른 국내 Top line 호조, 중국회복, 미국 실적 기여도 증가하는 점 긍정적이나 국내 믹스 변화에 따른 제한적인 마진개선 여력은 다소 아쉬움 맹진규 기자 maeng@hankyung.com

- 뉴스 > 증권

- 바로가기

-

中, 차세대 핵 잠수함 진수…美와 수중전력 격차 좁힌다 2026-02-23 17:19:33

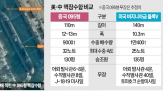

093형과 비슷하지만 선폭은 10m에서 12~13m로 넓어진 것으로 추정된다. 배수량도 093형의 7000t 수준에서 9000t 이상으로 늘어난 것으로 분석된다. 095형에서 가장 눈에 띄는 변화는 X자형 꼬리 방향타다. 중국 핵잠수함 가운데 이 같은 설계를 도입한 것은 처음으로, 기동성과 안정성을 높였다는 분석이다. 095형은 새로운...

- 뉴스 >

- 바로가기

-

미국, 이란 압박 풀가동…세계 최대 '슈퍼 핵항모' 추가 급파(종합) 2026-02-13 18:06:14

꼽힌다. 포드호는 2017년 공식 취역했다. 전장 약 351m, 선폭 약 41m(비행갑판 80m)에 비행기를 75대 이상 탑재할 수 있는 세계 최대 규모 항모다. 건조 비용만 약 133억달러(약 19조원)가 투입된 포드호는 신형 핵발전 플랜트, 통합 전쟁 시스템, 이중 대역 레이더 등 최첨단 기술이 적용돼 '슈퍼 핵 항모'로...

- 뉴스 > 정치

- 바로가기

-

'한국항공우주' 52주 신고가 경신, 개발에서 양산으로 - BNK투자증권, 보유 2026-02-13 10:34:10

것으로 전망된다. 다만 미래 먹거리를 위한 경상개발비(2026년 약 1,600억 원 계획) 투자가 지속되고, 초기 양산 단계의 비용 부담으로 인해 단기적으로 영업이 익률 개선폭은 제한적일 가능성이 있다."이라고 분석하며, 투자의견 '보유', 목표주가 '170,000원'을 제시했다. 한경로보뉴스 이 기사는 한국경제신문과 금융 AI...

- 뉴스 > 증권

- 바로가기

-

3D 메모리 시대 겨냥 넥스틴, 차세대 검사 솔루션 공개 2026-02-12 15:08:15

검출에 최적화된 솔루션이다. 넥스틴 관계자는 "최근 반도체칩의 선폭 미세화 한계 도달로 칩을 쌓고 직접 연결하는 3D 적층이 필수적으로 부상하면서 본딩 공정 시 수율과 직결되는 미세 보이드(Micro-void) 또한 주목을 받고 있다"고 설명했다. 보이드는 표면 오염물(Particle), 구리 패드의 높낮이 차이(Dishing) 등으로...

- 뉴스 > 산업

- 바로가기

-

'LG유플러스' 52주 신고가 경신, 수익과 성장에 발판 마련 - BNK투자증권, 매수 2026-02-05 15:47:55

배당에서 주주환원 확대 의지를 보인 만큼 실적 개선폭이 커질 2026년에는 더 확대할 것으로 전망한다."이라고 분석하며, 투자의견 '매수', 목표주가 '19,000원'을 제시했다. 한경로보뉴스 이 기사는 한국경제신문과 금융 AI 전문기업 씽크풀이 공동 개발한 기사 자동생성 알고리즘에 의해 실시간으로 작성된 것입니다.

- 뉴스 > 증권

- 바로가기

-

일본, 반도체 재건 '액셀'…TSMC 3나노 양산·라피더스 민간자금 확보 2026-02-05 14:21:43

사업 계획 변경을 협의할 계획이다. 나노는 반도체 회로 선폭을 의미하는 단위다. 선폭이 좁을수록 소비전력이 줄고 처리 속도가 빨라진다. TSMC는 3나노 제품을 대만에서만 생산하고 있다. 내년부터는 미국에서도 만들 계획이다. TSMC의 방침 변경으로 설비 투자액은 기존 122억 달러(약 17조8000억원)에서 170억 달러(약...

- 뉴스 > 정치

- 바로가기

-

日반도체 재건 가속…TSMC 3나노 양산·라피더스 민간자금 확보(종합) 2026-02-05 13:57:21

회로 선폭을 의미하는 단위로, 선폭이 좁을수록 소비전력이 줄고 처리 속도가 빨라진다. TSMC는 3나노 제품을 대만에서만 생산하고 있으며 내년부터 미국에서도 만들 계획이다. TSMC의 방침 변경으로 설비 투자액은 기존 122억 달러(약 17조8천억원)에서 170억 달러(약 24조8천억원)로 늘어날 것으로 전망된다고 요미우리가...

- 뉴스 > 정치

- 바로가기